electronique-news.com

03

'26

Written on Modified on

Solutions de sécurité post-quantique présentées à Embedded World 2026

SealSQ présentera lors du salon Embedded World 2026 ses dernières avancées en cryptographie post-quantique (PQC).

www.sealsq.com

L'émergence de l'informatique quantique menace de rendre obsolètes les algorithmes de chiffrement actuels. En collaboration avec Lattice Semiconductor et sa filiale IC’Alps, la société propose une architecture unifiée capable de protéger les systèmes embarqués, des dispositifs médicaux aux infrastructures énergétiques, contre les futures cyberattaques quantiques.

Solutions matérielles et cryptographie native

La stratégie de SealSQ repose sur l'intégration de la sécurité directement au niveau du silicium, garantissant une racine de confiance (Root of Trust) inviolable dès la fabrication :

Solutions matérielles et cryptographie native

La stratégie de SealSQ repose sur l'intégration de la sécurité directement au niveau du silicium, garantissant une racine de confiance (Root of Trust) inviolable dès la fabrication :

- QVault TPM : Une puce de sécurité conforme aux standards du Trusted Computing Group (TCG). Elle assure le stockage sécurisé des clés, le démarrage vérifié (Secure Boot) et l'intégrité continue des plateformes industrielles.

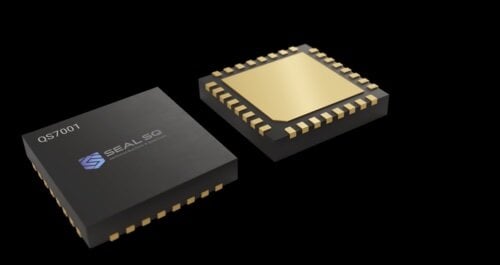

- QS7001 (RISC-V) : Un microcontrôleur basé sur l'architecture ouverte RISC-V, intégrant nativement les algorithmes PQC sélectionnés par le NIST. Il est optimisé pour les unités de contrôle (ECU) automobiles et la robotique.

- Architecture TPM-FPGA : Développée avec Lattice Semiconductor, cette solution démontre comment une sécurité résistante au quantique peut être injectée dans des circuits reprogrammables complexes.

Design ASIC sur mesure avec IC’Alps

La filiale IC’Alps complète cette offre en proposant des services de conception de circuits intégrés spécifiques (ASIC) et de System-on-Chip (SoC) personnalisés. Cette expertise permet aux industriels de miniaturiser leurs solutions tout en maximisant la performance et la protection de la propriété intellectuelle :

La filiale IC’Alps complète cette offre en proposant des services de conception de circuits intégrés spécifiques (ASIC) et de System-on-Chip (SoC) personnalisés. Cette expertise permet aux industriels de miniaturiser leurs solutions tout en maximisant la performance et la protection de la propriété intellectuelle :

- Co-design et Spécification : Accompagnement de l'architecture jusqu'à la production avec des fonderies leaders (TSMC, Intel Foundry, GlobalFoundries).

- Sécurité Renforcée : Intégration d'IPs cryptographiques durcies et préparation aux normes PQC pour des domaines sensibles comme les implants médicaux ou l'e-mobilité.

- Gestion du Cycle de Vie : Services PKI pour la personnalisation "zero-touch" et la mise à jour sécurisée des flottes de dispositifs IoT à grande échelle (compatible AWS, Azure, Matter).

Les visiteurs d'Embedded World pourront assister à des démonstrations du design de référence post-quantique sur le stand de Lattice (Hall 4, Booth 528) et dévouvrir l'écosystème de SealSQ du 10 au 12 mars 2026 à Nuremberg.

www.sealsq.com

www.sealsq.com