electronique-news.com

08

'21

Written on Modified on

Générer du courant à moins de 1 V

L’électronique numérique a connu une progression phénoménale, tant en matière de performances que d’exigences d’alimentation. Souvenons-nous du premier microprocesseur8086, avec sa fréquence maximale de 10 MHz et sa finesse de gravure de 3 µm.

Il utilisait 5 V pour les fonctions de base et d’E/S, mais ne dissipait que 1,8 W. Tout au long de sa durée de vie, ce circuit d’alimentation «à plan unique» est progressivement passé de 5 à 3,3V. Avec l’arrivée des ordinateurs portables et des terminaux mobiles, il a fallu réduire la consommation d’énergie. C’est ce qui a poussé à passer à une conception à double plan qui permettait au noyau de fonctionner à une tension plus basse tandis que l’E/S restait à 3,3V. De nos jours, les microprocesseurs cadencés à 4GHz ont une finesse de gravure de 7nm avec une alimentation à moins de 1V et une puissance de crête d’environ 140watts.

Réduire la tension permet de réduire la consommation d’énergie, mais cela réduit aussi la vitesse des processeurs. Des tensions plus élevées sollicitent les isolants d’oxyde métallique dans les transistors du processeur et augmentent les fuites et la perte de puissance en raison de « l’effet tunnel ». L’épaisseur de la couche d’isolation n’est généralement que de 0,5 nm, soit environ la taille de deux atomes. Afin de fournir des performances toujours plus élevées, mais à des tensions d’alimentation faibles, le traitement parallèle dans des processeurs multicœurs exécutant plusieurs threads de code est devenu la norme, ce qui entraîne une multiplication de la puissance globale et de la consommation électrique.

Une alimentation électrique centralisée convenait pour les conceptions à plan unique. Les circuits intégrés conservaient leur précision avec la réduction à de faibles tensions des connexions à faible courant. Plus les tensions étaient basses, plus le courant augmentait et plus les spécifications de précision devenaient strictes. L’architecture « à bus intermédiaire » s’est alors imposée pour acheminer la tension dans un système à un niveau plus élevé, généralement 12 V, et à un courant plus faible. Ensuite, un convertisseur CC-CC réduisait la tension au niveau de fonctionnement proche de la charge.

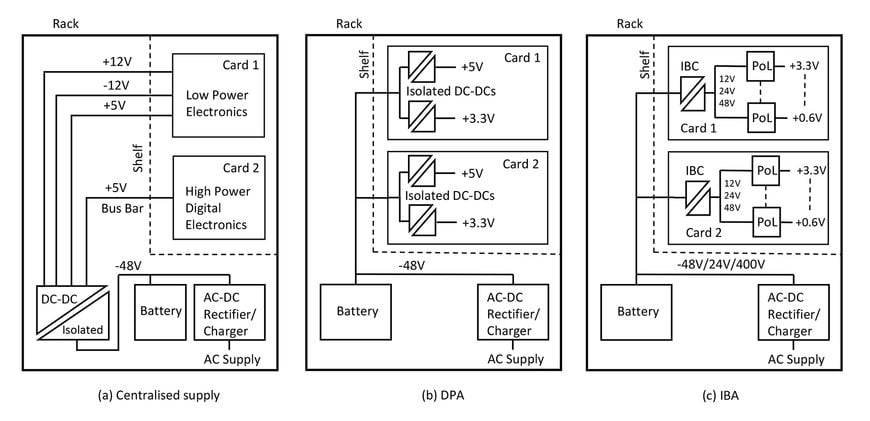

Dans les environnements de télécommunications, les alimentations doivent à la fois être fiables et permettre de réduire à un minimum les coûts financiers et environnementaux. De ce fait, l’évolution constante de la technologie informatique a soumis les alimentations à d’importants changements en termes d’architecture. Jusqu’au début des années 1990, les alimentations centralisées étaient la norme, avec un redresseur CA-CC générant un bus 48 V doté d’une pile de sauvegarde (voir figure 1a). Un convertisseur CC-CC fournissait ensuite des tensions plus faibles, généralement 5 V et +/-12 V aux étagères des armoires. La régulation statique et dynamique était médiocre et la panne d’un seul composant pouvait mettre l’ensemble du système hors d’usage. C’est pourquoi l’architecture d’alimentation distribuée (DPA) a été conçue. Celle-ci permet d’acheminer 48 V avec sauvegarde sur pile à chaque étagère avec des convertisseurs CC-CC isolés sur des cartes qui fournissent les tensions finales (figure 1b). Les cartes redondantes pouvaient dès lors être remplacées à chaud, le système continuant de fonctionner grâce à une régulation de tension serrée au niveau des charges. Parce que de nombreux convertisseurs CC-CC isolés augmentaient aussi les coûts, il a parfois été fait usage d’architectures hybrides centralisé/DPA.

L’évolution suivante a été l’architecture à bus intermédiaire (IBA) (voir figure 1c), où l’isolation et la conversion en une tension intermédiaire de 5 V ou 12 V sont assurées par un convertisseur de bus (IBC) unique sur chaque carte. Des convertisseurs CC-CC ou points de charge (PoL) non isolés et peu coûteux fournissent ensuite la tension finale. Le convertisseur de bus était alimenté par du 48 V, 24 V ou même 400 V afin de maintenir le courant primaire et les pertes de conduction à faible niveau. En fonction de l’application, le convertisseur pouvait être entièrement régulé, semi-régulé ou non régulé, car les convertisseurs PoL sont généralement à entrée large et n’ont pas besoin d’une alimentation strictement régulée.

Architectures de puissance modernes

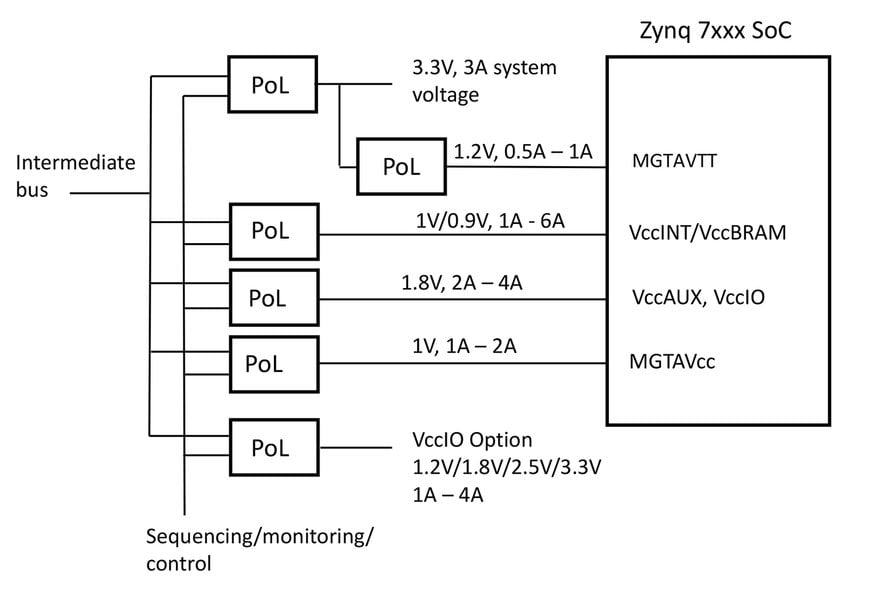

L’IBA est aujourd’hui une architecture courante, avec des variantes de convertisseurs de bus conçus pour fournir le meilleur rendement global dans l’application visée. Cependant, les charges n’ont cessé d’augmenter et les tensions de bus intermédiaires de 12 V ont commencé à poser des problèmes avec les courants élevés. C’est ainsi que les conceptions plus récentes ont tendance à augmenter le bus à 48 V et à spécifier des convertisseurs PoL pour réduire cette tension, parfois de façon extrême directement à moins de 1 V. Le rapport de conversion élevé produit des impulsions courtes et des courants de pointe élevés dans le convertisseur, ce qui, il y a quelques années encore, était considéré comme peu pratique pour des raisons de rendement. Or, les semi-conducteurs et les topologies de conversion de puissance ayant depuis progressé, cette approche est désormais considérée comme viable, en particulier lorsque l’on tient compte de la réduction des pertes ohmiques, de la taille et du coût du bus. Lorsque cela est justifié pour des raisons de rendement, on utilise alors des étages en cascade de PoL : par exemple de 48 V au 3,3 V requis pour les E/S, alimentant un autre PoL de 3,3 V à 1,8 V. Les concepteurs de systèmes produisent un « arbre de puissance » pour représenter leur architecture proposée. La figure 2 en présente un exemple pour un système sur puce (SoC) Xilinx.

un « arbre de puissance » pour un appareil SoC Xilinx.

Spécifications des PoL

Les PoL utilisés pour l’IBA doivent répondre à des spécifications strictes en ce qui concerne le bruit de sortie, la tolérance de tension et la régulation statique et dynamique. De manière générale, il est requis de maintenir la sortie dans une plage de +/-3 % dans toutes les conditions pour les charges les plus sensibles, telles que les DSP fonctionnant avec une alimentation de 1 V avec des paliers de charge de 5 A ou plus. Puisque la boucle de commande du convertisseur doit être rapide, la fréquence de commutation est élevée, ce qui oblige à utiliser des semi-conducteurs à haute performance, notamment ceux de types récents à large bande interdite afin d’obtenir un meilleur rendement. Le PoL doit pouvoir être « séquencé » avec d’autres PoL de sorte que les rails d’alimentation montent et descendent dans le bon ordre. De plus en plus souvent, le processeur doit pouvoir communiquer avec le PoL afin d’assurer l’ajustement dynamique de la tension de sortie et la surveillance des performances (courant de sortie, température, indicateurs de défaut…), généralement à l’aide de commandes PMBus sur une interface I2C. Les PoL de dernière génération comportent également un contrôle de boucle numérique pour des performances optimales avec des charges changeantes et une capacité de sortie variable pour différentes applications ou lorsque les conditions changent avec le temps. Le contrôle et la surveillance dans un PoL sont par conséquent des tâches compliquées à assurer. Même la topologie de base d’un convertisseur abaisseur classique se voit enrichie par un redressement synchrone et un fonctionnement multiphase afin d’obtenir un rendement acceptable à des courants de charge élevés tout en maintenant de faibles pertes de charge légère.

Les spécifications des convertisseurs PoL varient quelque peu avec la charge. Les CPU, les FPGA, les ASICS, les SoC et les périphériques ACAP ont tous leurs exigences particulières. Dans tous les cas, il faut installer le convertisseur au plus près de la charge afin d’obtenir les meilleures performances possible. Or, cela crée un problème d’agencement de la carte avec la multitude de lignes d’adresses et d’E/S qui doivent être supportées. Les PoL doivent donc être très compacts et c’est pour cette raison que les versions à composants discrets des PoL sont rarement viables. Les modules s’imposent dès lors comme un choix logique. Cette approche présente également l’avantage de permettre l’utilisation de plus d’espace vertical avec des pièces prétestées et certifiées et avec des empreintes conformes aux normes de l’industrie. La technologie requise dans les PoL nécessite également des agencements de carte méticuleux pour les plans d’alimentation, les couches de protection et les boucles de courant serrées dans l’étage de puissance pour l’atténuation des interférences électromagnétiques. Ces fonctionnalités sont plus faciles à implanter dans le substrat d’un module dédié à la tâche que dans la carte mère. Avec un PoL classique comprenant plus de 100 composants, le stockage et l’approvisionnement d’un module sont également beaucoup plus simples qu’avec une solution discrète.

Il est possible de recourir à de solutions hybrides lorsque l’étage de puissance est disponible sous la forme d’un module compatible avec les circuits intégrés de gestion de l’alimentation et de contrôle de fabricants tiers. Dans ce cas, le CI est placé sur la carte mère et le module est placé par-dessus ou parfois sur le côté opposé de la carte mère.

Formats de PoL – les alternatives

Les convertisseurs PoL sont disponibles aux formats SIP traversants ou enfichables afin d’occuper un minimum d’espace sur la carte. Ce type de PoL est disponible chez de nombreux fabricants comme Texas Instruments, RECOM, CUI, TRACO, Murata, ABB, XP Power, Advanced Energy, etc. Afin de réaliser des économies sur le coût de fabrication, on optera pour des modules montés en surface. Plusieurs options de montage existent : Gullwing, pieds carrés, LGA et iLGA (Inspectable Land Grid Array). Les sorties sont disponibles jusqu’à des fractions de volt et à courants pouvant dépasser les 40 A.

plusieurs exemples de formats de PoL : à gauche, série TI TPSM ; au milieu, série CUI V78E ; à droite, série Murata MYMG.

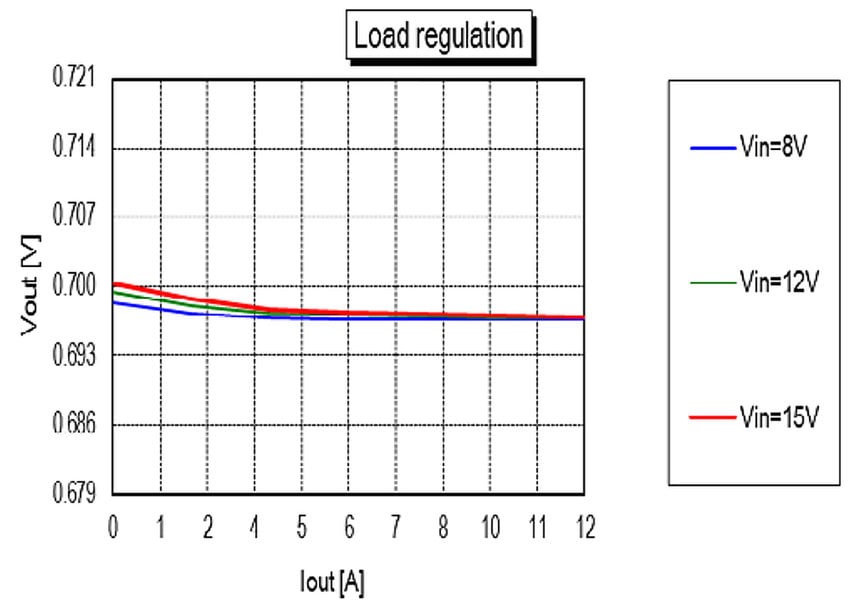

À titre d’exemple, la série « monobloc » MYMGA de Murata fournit 12 A depuis un boîtier LGA de seulement 10,5 x 9,0 x 5,6 mm. Ces composants présentent des plages d’entrée de 4,5 à 8 V ou de 8 à 15 V et la sortie peut être ajustée de 0,7 à 1,8 V avec un rendement atteignant les 93,5 %. Conformément aux exigences des FPGA/CPU pour des rails de tension précis, cette gamme a une régulation de charge maximale de +/-1 % (voir figure 4).

les différents modèles MYMGA de Murata ont une régulation de charge de +/-1 %.

Le PTH08T250Wde Texas Instruments est un convertisseur PoL au format traversant. Il dispose lui aussi d’une régulation de charge serrée de +/-1,5 %, mais sur la plage de charge de sortie de 0 à 50 A avec la possibilité de mettre les modules en parallèle pour des courants encore plus élevés. Ce composant a une plage d’entrée de 4,5 à 14 V et une sortie réglable entre 0,7 V et 3,6 V et jusqu’à 96 % de rendement. Les composants Murata et Texas Instruments conviennent aux architectures à bus intermédiaire (IBA) où la tension du bus est faiblement régulée, ce qui résulte en un meilleur rendement global.

Tous les convertisseurs disposent de fonctions de protection complètes et certains sont conformes aux normes de performances et de brochage définies par la DOSA (Distributed-power Open Standards Alliance). Une caractéristique intéressante est la possibilité de démarrer dans des charges prépolarisées, ce qui peut se produire dans des systèmes à plusieurs rails de tension. Les convertisseurs PoL plus complexes offrent plus de fonctions de surveillance et de contrôle, comme la fonction « Tunable Loop » proposée dans lasérie Lynxd’ABB, et qui permet à l’utilisateur d’ajuster la boucle de contrôle de tension pour maximaliser les performances dynamiques tout en réduisant au minimum la capacité de sortie pour toute charge particulière.

La plupart des fournisseurs de PoL modulaires proposent des cartes de démonstration avec des interfaces graphiques pour configurer la réponse en boucle et les paramètres de contrôle et de surveillance.

Résumé

Grâce à leurs performances incroyables, les processeurs modernes et les circuits intégrés programmables sont désormais omniprésents : de l’infodivertissement aux télécommunications en passant par l’industrie. Alimenter ces processeurs avec des tensions toujours plus faibles et des courants toujours plus élevés constituait un véritable défi que les concepteurs de convertisseurs CC-CC ont su relever, en particulier avec les convertisseurs PoL modulaires qui s’intègrent aux architectures de bus afin d’obtenir des rails de tension propres et à hautes performances avec un rendement de conversion élevé. De plus, les convertisseurs PoL constituent une solution économique par rapport aux composants discrets. L’intelligence intégrée offre un avantage supplémentaire en adaptant les performances des PoL aux exigences de charge et en ajoutant des commandes de contrôle et la signalisation d’état.

www.mouser.fr