electronique-news.com

27

'22

Written on Modified on

RISC-V : l’ISA open source, libre et extensible qui booste l’industrie

Teaser long : Le dernier bouleversement notable remonte à l’époque où ARM se mit à développer des cœurs qu’elle commercialisa sous licence IP, ce qui eut pour effet immédiat de changer la façon de concevoir des processeurs des principaux fondeurs d’alors.

Ce n’est pas tous les jours que l’industrie des processeurs à semiconducteurs voit apparaître une nouvelle architecture de jeu d’instructions (ou ISA, pour « instruction set architecture »).

Alors que nous nous trouvons maintenant dans une ère de guerre commerciale et de pandémie, la mise à disposition d’une ISA open source, libre et extensible est un événement disruptif qui promet bien des transformations.

Teaser court : Les architectures de jeu d’instructions (ISA) ont peu changé au cours des quarante dernières années. Dès lors, l’arrivée d’une ISA open source, libre et extensible comme RISC-V a eu l’effet d’un séisme dans l’industrie des processeurs.

Mots clés SEO : x86, MIPS, ISA, architecture de jeu d’instructions, RISC, CISC, RISC-V, Microchip, AVR, Atmel, Atmel AVR, ARM, Intel, SoC, FPGA, SparkFun, SEEED

L’ISA des processeurs a connu peu de changements en 40 ans

Depuis des décennies, le paysage de l’architecture des processeurs est dominé par Intel et ARM. La première de ces sociétés, avec son architecture x86, règne sur le marché des postes de travail, des ordinateurs de bureau et des serveurs, tandis qu’ARM s’est emparé d’un plus large marché encore en équipant la majorité des appareils IoT, de l’électronique grand public et des systèmes d’automatisation industrielle. D’autres architectures destinées aux processeurs et microcontrôleurs embarqués, comme l’AVR d’Atmel et le PIC/MIPS de Microchip, ont su trouver leur place dans un marché de niche, mais sont loin d’atteindre la masse critique des acteurs dominants précités.

Le modèle économique d’ARM, qui repose sur la conception de propriétés intellectuelles (ou licences IP), a été largement adopté par la plupart des fournisseurs de microcontrôleurs (MCU) et de microprocesseurs (MPU) dans le domaine de l’embarqué. Or, ces normes bien établies semblent aujourd’hui remises en question par un événement disruptif qui n’a pas tardé à changer la donne, à savoir l’arrivée sur le marché de l’ISA open source RISC-V. Les principaux fabricants se sont rapidement tournés vers cette nouvelle ISA, faisant ainsi profiter les consommateurs finaux des avantages commerciaux et technologiques inhérents à une architecture ouverte. Dans cet article, nous allons tout d’abord brièvement retracer l’histoire de RISC-V et mettre en lumière quelques-uns des facteurs du succès de cette nouvelle architecture. Nous passerons également en revue quelques exemples de produits en nous attardant plus particulièrement sur les cartes d’évaluation, les ressources de développement et l’écosystème croissant de chaînes d’outils logiciels.

L’ISA : Le maillon indispensable entre matériel et logiciel

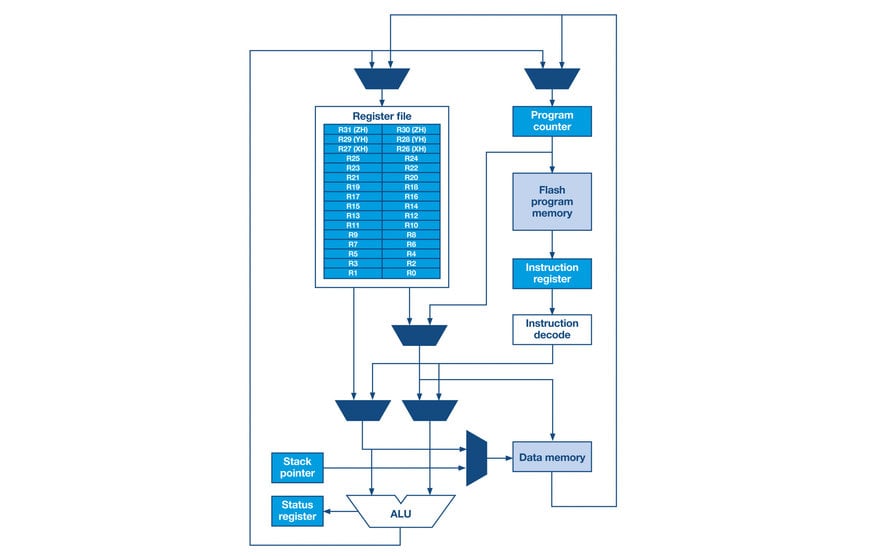

L’architecture de jeu d’instructions (ISA) jette un pont entre deux mondes en fournissant l’interface entre le logiciel et le matériel d’un processeur. L’ISA définit chaque aspect de la façon dont un programme interagit avec le matériel disponible, dont l’unité arithmétique et logique (ALU), les registres, la mémoire et la logique de commande. Elle spécifie également la longueur des mots, les types de données pris en charge et la façon dont les registres et les emplacements mémoire sont adressés. Bref, une ISA est un résumé de processeur.

Il existe de nombreux types d’ISA, mais, pour des raisons pratiques, les deux principaux types sont les ordinateurs à jeu d’instruction complexe (CISC) et les processeurs à jeu d’instructions réduit (RISC). Comme son nom l’indique, un CISC comprend de nombreuses instructions complexes et spécialisées pour diverses applications, certaines n’étant que rarement utilisées. Un processeur de type CISC propose également de nombreuses méthodes d’adressage et utilise des instructions de longueurs variables. Les processeurs CISC sont coûteux et longs à concevoir, car ils nécessitent des logiciels et des outils de programmation plus sophistiqués. Un exemple d’ISA CISC est l’Intel x86.

Les processeurs basés sur l’architecture RISC sont quant à eux beaucoup plus simples. Ils possèdent un ensemble limité d’instructions fréquemment utilisées, quelques modes d’adressage différents et une taille d’instruction fixe. L’utilisation de pipelines d’instructions offre un débit d’exécution plus rapide. Contrairement à un processeur CISC qui déplace des opérandes (valeurs de données) vers la mémoire pour effectuer des calculs, un processeur RISC utilise des registres internes. ARM, AVR, PIC et MIPS sont des exemples d’ISA RISC.

Exemple d’architecture RISC d’un microcontrôleur Microchip AVR.

Quels sont les facteurs clés de réussite pour une ISA ?

Nous nous intéresserons, dans la suite de cet article, exclusivement aux processeurs basés sur une architecture RISC, et par processeur, nous entendons tout dispositif de traitement, microcontrôleurs comme microprocesseurs. Les ISA RISC populaires sont disponibles avec des longueurs de mots de 8, 16 ou 32 bits. Les ISA à 64 ou 128 bits sont généralement utilisées pour des applications spécialisées et plus exigeantes. La longueur des mots a une incidence directe sur la conception du matériel, la vitesse de fonctionnement du processeur et la taille de la mémoire disponible. Une ISA doit comprendre au minimum une unité arithmétique et logique (ALU), de la mémoire et une logique de commande. L’ALU exécute les opérations arithmétiques de base (addition, soustraction, etc.) et les comparaisons à l’aide de registres ou par soi-même à la volée. L’adressage mémoire peut être absolu ou indexé. La logique de commande réalise des branchements conditionnels et inconditionnels et d’autres tâches d’adressage.

Le jeu d’instructions d’une ISA se compose de codes opérations (opcodes) qui spécifient la tâche à effectuer, généralement sur un ou plusieurs opérandes. Par exemple, dans l’ISA des cœurs AVR d’Atmel/Microchip, le convertisseur analogique-numérique définit l’addition d’opérandes contenus dans deux registres avec un indicateur de retenue et place le résultat dans le registre de destination. La documentation ISA indique combien de cycles d’horloge ou d’itérations de compteur de programme chaque instruction nécessite. Dans un processeur RISC, la majorité des instructions seront à cycle unique.

Pour les fournisseurs de microcontrôleurs (MCU) et de microprocesseurs (MPU), le développement d’une ISA est une phase essentielle dans la conception de leurs produits. C’est ainsi que les ISA devinrent propriétaires, car elles étaient créées pour une série spécifique de dispositifs, comme les cœurs AVR d’Atmel/Microchip (8, 16, 32 bits), les microcontrôleurs PIC de Microchip (8, 16, 32 bits) ou encore les MIPS (32, 64 bits).

Lorsque la société ARM (pour Advanced RISC Machines) est arrivée sur le marché au début des années 90 en tant que filiale d’Acorn, son modèle économique a bouleversé le modèle traditionnel du secteur des MCU/MPU. L’entreprise s’est en effet orientée vers la conception de propriétés intellectuelles, tirant ainsi ses revenus non pas de la fabrication et de la vente de systèmes, mais du paiement de droits d’exploitation. Ce modèle a connu un rapide essor, car il permettait enfin aux fournisseurs de semiconducteurs de s’affranchir de la contrainte de développer et de porter eux-mêmes leur architecture propriétaire. De nos jours, la plupart des fondeurs proposent des processeurs basés sur l’ISA d’ARM – même si certains continuent de proposer en parallèle

des dispositifs basés sur leur propre ISA – et paient des droits à ARM pour chaque appareil vendu. En contrepartie, ARM assure le contrôle du cycle de vie et le développement continu de son architecture.

Bien que les architectures propriétaires aient toutes leurs avantages et leurs inconvénients, le succès d’une architecture processeur en particulier ne dépend pas seulement de ses mérites sur le plan technique, mais aussi de la disponibilité d’un écosystème d’outils de développement. Les chaînes d’outils, les environnements de développement intégrés, les compilateurs, les débogueurs et les intergiciels spécifiques aux applications sont des facteurs de réussite clés dans la popularité d’un processeur et de son ISA.

« Ouvrez » l’ISA !

Grâce à ARM, les sociétés de semiconducteurs disposaient d’une architecture standardisée autour de laquelle ils pouvaient adapter et améliorer les options d’interface des périphériques de l’appareil afin de convenir au mieux à des applications spécifiques. Cette approche leur a également permis de démarquer jusqu’à un certain point leurs produits par rapport à ceux de concurrents eux aussi sous licence IP d’ARM. D’autre part, la grande popularité de l’architecture ARM a fortement réduit la part de marché d’ISA pourtant bien établies comme AVR ou PIC.

Pour le consommateur, opter pour l’architecture ARM est une décision prudente, car ce ne sont pas les fournisseurs qui manquent, ce qui permet de choisir parmi de nombreuses possibilités lorsqu’il s’agit de se réapprovisionner en pièces similaires. De même, standardiser le développement autour d’une chaîne d’outils spécifique est une démarche censée sur le pan commercial.

Alors qu’il relève d’une industrie où le principe de la conception open source a largement cours, le domaine des architectures de jeu d’instructions conservait quant à lui un caractère nettement propriétaire. Ce fut au moins le cas jusqu’à l’apparition de RISC-V en 2010. Ce projet initialement développé dans un but académique à l’Université de Californie Berkeley a rapidement imposé le modèle de conception rendant l’ISA ouverte. Ce choix de l’open source était motivée par le constat que la conception des ISA avait peu changé au cours des quarante dernières années. Proposer une ISA ouverte inciterait dès lors à davantage d’interaction et de réutilisation des logiciels, avec l’espoir de bénéficier d’un support à long terme de la part des fournisseurs de la chaîne d’outils des sociétés de semiconducteurs. L’avantage d’une ISA ouverte est que les fournisseurs n’ont pas à reverser de droits d’exploitation et sont mêmes autorisés à créer de nouvelles instructions et extensions.

L’architecture RISC-V de base et les extensions qui y sont associées sont développées et gérées collectivement par la communauté de la recherche universitaire et l’industrie. RISC-V prend en charge des longueurs de mot de 32, 64 et 128 bits.

Une étape importante a été franchie en 2015, lorsqu’un consortium de sociétés de semiconducteurs a fondé la RISC-V Foundation. Le fait de ne pas devoir payer de droits et le caractère extensible de cette ISA ont su attirer l’attention des acteurs du marché. En effet, les sociétés détentrices d’une licence ARM ne peuvent pas modifier le jeu d’instructions afin de l’adapter à des applications spécifiques comme une alimentation de faible puissance par exemple. Or, la licence RISC-V le permet. La RISC-V Foundation compte aujourd’hui plus de 750 membres dans l’industrie des semiconducteurs.

Voyant l’intérêt grandissant que portaient de nombreuses grandes sociétés de semiconducteurs pour RISC-V, les développeurs d’outils logiciels n’ont pas voulu être en reste et fournissent désormais une prise en charge étendue de RISC-V avec leur IDE et leurs chaînes d’outils.

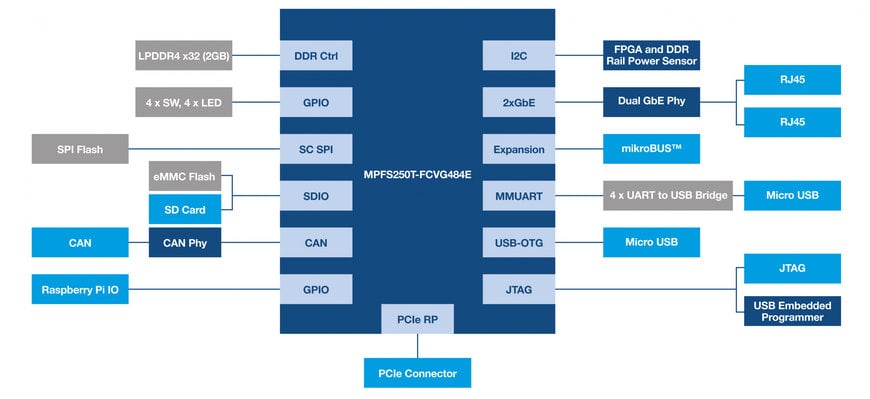

Schéma fonctionnel du kit d’évaluation SoC RISC-V PolarFire de Microchip.

Les premiers pas avec RISC-V

L’un des tout premiers processeur 32 bits à architecture RISC-V mis sur le marché fut le SoC Freedom E31 de SiFive. La société elle-même fut fondée par les créateurs de RISC-V, désireux de mettre leur expertise au service du marché. Afin d’encourager le prototypage, SiFive lança le financement participatif d’une carte de développement peu coûteuse avec facteur d’encombrement Arduino baptisée HiFive1. Aujourd’hui, la HiFive1 B de SiFive intègre une connectivité Wi-Fi et 32 Mo de mémoire flash.

Seeed Studio propose une carte de développement au format Feather/MKR, la Sipeed Longane Nano. Équipée d’un écran LCD de 0,96 pouces, elle est conçue autour d’un cœur RISC-V 32 bits GigaDevice.

SparkFun commercialise une carte de développement similaire à la HiFive1 B. Sa RED-V RedBoard s’appuie elle aussi sur le facteur d’encombrement Arduino UNO-R3 ainsi que le SoC E310 RISC-V de SiFive.

De son côté, avec la carte de développement PolarFire SoC FPGA Icicle

Conçu pour fournir une plateforme d’évaluation pour le processeur RISC-V RV64 à cinq cœurs compatible Linux, le SoC PolarFire est également équipé d’éléments logiques de 256 k et d’un bloc mathématique de 784 éléments. Idéal pour le prototypage de conceptions en temps réel à faible consommation d’énergie, des capteurs IoT aux applications d’apprentissage automatique, le kit Icicle comprend une connectivité d’interface périphérique complète, (HDMI, PCIe, USB, CAN, SPI et I2C). Notons également parmi les options d’extension d’interface une prise mikroBUS et un connecteur Raspberry Pi 40 broches.

RISC-V : Et ensuite ?

En une période relativement courte, l’architecture de jeu d’instructions RISC-V a su se tailler la part du lion. En 2020, la RISC-V Foundation a célébré le dixième anniversaire du développement initial de son ISA. Selon le site web de la fondation, pas moins de 12 SoC et 86 cœurs basés sur RISC-V sont désormais commercialisés.

RISC-V s’est rapidement imposé comme une alternative viable, extensible et libre de droits aux autres ISA.

www.mouser.com